# COAVL: A Virtual Lab on Computer Organization and Architecture

Chittaranjan Mandal with Gargi Roy and Devleena Ghosh Presenter: Partha De

Dept of Computer Sc & Engg IIT Kharagpur

> COAVL Presentation February 27, 2015

### Virtual lab objective and relevance

- COA is a core course in the curriculum of CSE, EE and ECE

- Laboratory experiments essential to understanding basics

- Most places used bread board based setup

#### Drawbacks

- Limits the size and extent of experiments

- 2 Time consuming

#### Virtual lab objective and relevance

- COA is a core course in the curriculum of CSE, EE and ECE

- Laboratory experiments essential to understanding basics

- Most places used bread board based setup

# Limits the s

extent of experiments

2 Time consuming

C Mandal, G Roy, D Ghosh (IIT Kharagpur COAVL: A Virtual Lab on Computer Organia

COAVL-27February2015

2 / 36

#### Virtual lab objective and relevance

- COA is a core course in the curriculum of CSE, EE and ECE

- Laboratory experiments essential to understanding basics

- Most places used bread board based setup

2 / 36

### Virtual lab objective and relevance contd..

- FPGA based lab to overcome this limitation

- Also has some limitations:

- Learning curve with FPGAs somewhat high

- Expensive

- Logistics barrier of running lab

- Hence virtual lab, especially for most institutions

# Experiments designed using concept hierarchy

#### **Computer Arithmetic related**

- Design of a Ripple Carry Adder

- Design of a Carry-Look-Ahead Adder

- Design of Wallace Tree Adder

- Synthesis of flip-flops

- Design of Registers and Counters

- Design of Combinational Multipliers

- Design of Booth's Multiplier

- Design of an ALU

#### Memory related

- Design of Memory elements

- Design of Associative cache without replacement policy

- Design of Direct Mapped cache without replacement policy

#### **CPU** design related

Design of single instruction CPU

4 / 36

### Web interface of COLDVL

- Pedagogic considerations are reflected in web interface

- Web interface includes set of experiments, manual, others

#### Web interface of each experiment

- Theory

- Objective

- Guideline to check key behavior of the design

- Test plan

- Assignments

- Procedure

- Experimentation platform (generic simulation platform)considered

- Quizzes

- Further reading

团

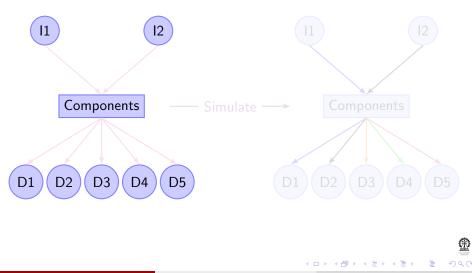

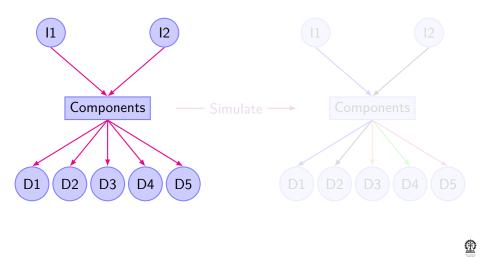

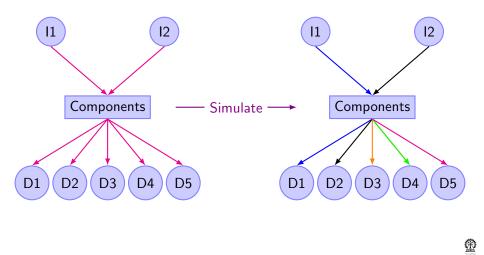

#### Features of the COAVL simulator

- The simulator supports 5-valued logic [True(T)(wire color: blue) False(F)(wire color: black) High impedence(Z)(wire color: green) Unknown(X)(wire color: maroon) Invalid(I)(wire color: orange) ]

- Capable of simulating combinational circuits and synchronous sequential circuits

- Control signal generation from a user given ASM chart

- Bus based design with wired AND operation to CPU design

- Includes a single instruction CPU design with built-in controller

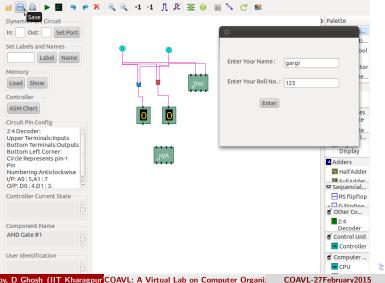

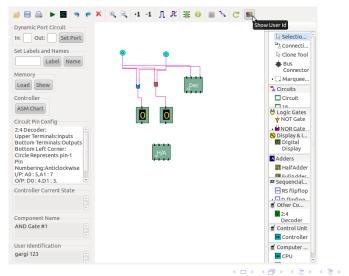

- Saving with Identification to check plagiarism

- Circuit analysis through different wire colors

- Minimal server dependency by having client side simulation

COAVL-27February2015

The simulator has the following:

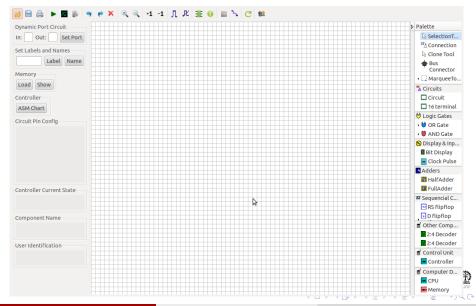

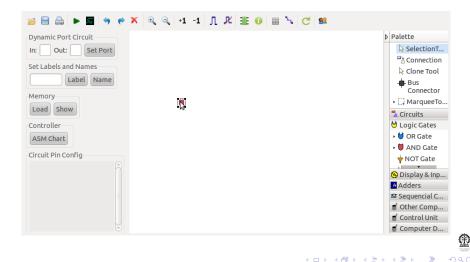

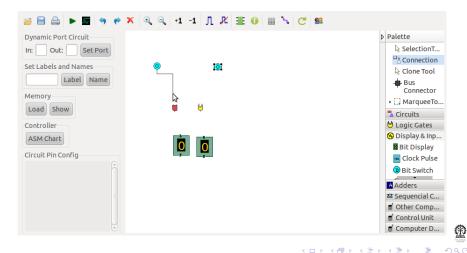

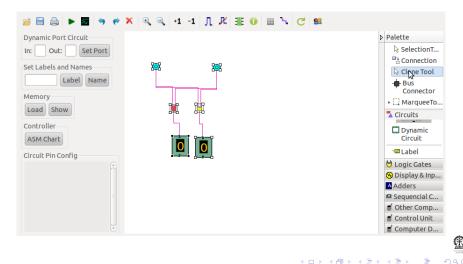

#### **Graphical editor**

- A canvas to design the circuit

- Click and Drop method to add the components

- Different functional buttons like undo/redo, delete, zoom, save/open, print, showing timing diagram etc.

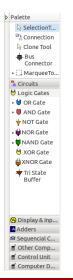

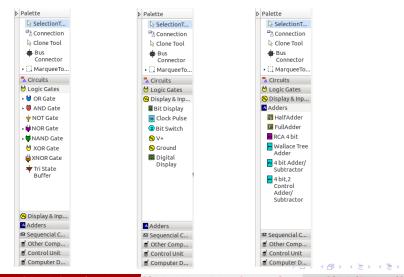

#### Palette

- Tools like connection, selection, clone

- All types of logic gates and flip-flops

- Inputs including free running clock

- Display units

- Adders, decoders, multiplexers, registers, counters etc.

- Arithmetic logic units, memory elements including cache memory

- Controller

- Other complex components like single instruction CPU, 4 bit address working memory etc.

COAVL-27February2015

7 / 36

The simulator has the following:

#### **Graphical editor**

- A canvas to design the circuit

- Click and Drop method to add the components

- Different functional buttons like undo/redo, delete, zoom, save/open, print, showing timing diagram etc.

Palette

- Tools like connection, selection, clone

- All types of logic gates and flip-flops

- Inputs including free running clock

- Display units

- Adders, decoders, multiplexers, registers, counters etc.

- Arithmetic logic units, memory elements including cache memory

- Controller

- Other complex components like single instruction CPU, 4 bit address working memory etc.

COAVL-27February2015

7 / 36

C Mandal, G Roy, D Ghosh (IIT Kharagpur<mark>)</mark>COAVL: A Virtual Lab on Computer Organi.

The simulator has the following:

#### **Graphical editor**

- A canvas to design the circuit

- Click and Drop method to add the components

- Different functional buttons like undo/redo, delete, zoom, save/open, print, showing timing diagram etc.

#### Palette

- Tools like connection, selection, clone

- All types of logic gates and flip-flops

- Inputs including free running clock

- Display units

- Adders, decoders, multiplexers, registers, counters etc.

- Arithmetic logic units, memory elements including cache memory

- Controller

- Other complex components like single instruction CPU, 4 bit address working memory etc.

COAVL-27February2015

7 / 36

The simulator has the following:

#### **Graphical editor**

- A canvas to design the circuit

- Click and Drop method to add the components

- Different functional buttons like undo/redo, delete, zoom, save/open, print, showing timing diagram etc.

#### Palette

- Tools like connection, selection, clone

- All types of logic gates and flip-flops

- Inputs including free running clock

- Display units

- Adders, decoders, multiplexers, registers, counters etc.

- Arithmetic logic units, memory elements including cache memory

- Controller

- Other complex components like single instruction CPU, 4 bit address working memory etc.

COAVL-27February2015

7 / 36

The simulator has the following:

#### **Graphical editor**

- A canvas to design the circuit

- Click and Drop method to add the components

- Different functional buttons like undo/redo, delete, zoom, save/open, print, showing timing diagram etc.

#### Palette

- Tools like connection, selection, clone

- All types of logic gates and flip-flops

- Inputs including free running clock

- Display units

- Adders, decoders, multiplexers, registers, counters etc.

- Arithmetic logic units, memory elements including cache memory

- Controller

- Other complex components like single instruction CPU, 4 bit address working memory etc.

C Mandal, G Roy, D Ghosh (IIT Kharagpur)COAVL: A Virtual Lab on Computer Organi:

COAVL-27February2015 8 / 36

⊉

C Mandal, G Roy, D Ghosh (IIT Kharagpur COAVL: A Virtual Lab on Computer Organi. COAVL-27February2015

9 / 36

э

< ロ > < 同 > < 回 > < 回 >

C Mandal, G Roy, D Ghosh (IIT Kharagpur<mark>)COAVL: A Virtual Lab on Computer Organi: C(</mark>

3

< ロ > < 同 > < 回 > < 回 >

嬼

C Mandal, G Roy, D Ghosh (IIT Kharagpur)COAVL: A Virtual Lab on Computer Organi:

э

嬼

C Mandal, G Roy, D Ghosh (IIT Kharagpur COAVL: A Virtual Lab on Computer Organia

COAVL-27February2015

9 / 36

### Component drawers contd..

⑳

C Mandal, G Roy, D Ghosh (IIT Kharagpur<sup>C</sup>COAVL: A Virtual Lab on Computer Organi: COAVL-27February2015

10 / 36

э

< ロ > < 同 > < 回 > < 回 >

#### Component drawers contd..

C Mandal, G Roy, D Ghosh (IIT Kharagpur)COAVL: A Virtual Lab on Computer Organi:

< ロ > < 同 > < 回 > < 回 >

# Component drawers contd..

C Mandal, G Roy, D Ghosh (IIT Kharagpur COAVL: A Virtual Lab on Computer Organi

COAVL-27February2015

10 / 36

Ð

(日)

э

- ∢ ⊒ →

C Mandal, G Roy, D Ghosh (IIT Kharagpur COAVL: A Virtual Lab on Computer Organi: COAVL-27February2015 11 / 36

(日)

э

- ∢ ⊒ →

э

A B F A B F

< □ > < 同 >

# Building a haff adder circuit

To instantiate a component left click on the component icon

| 📸 🔚 🖕 🖿 🧑 🥐 🗙 🔍 🔍 +1 -1 👖 🕂 🎚 🕖 🏢 🍾 🥑 😫 |                                                                                    |

|-----------------------------------------|------------------------------------------------------------------------------------|

| Dynamic Port Circuit                    | Palette                                                                            |

| In: Out: Set Port                       | SelectionT                                                                         |

|                                         | <sup>□</sup> Connection                                                            |

| Set Labels and Names                    | Clone Tool                                                                         |

| Label Name                              | - Bus<br>Connector                                                                 |

| Memory                                  | • 🖸 MarqueeTo                                                                      |

| Load Show                               | Circuits                                                                           |

| Controller                              | 💆 Logic Gates                                                                      |

| ASM Chart                               | 🔸 💆 OR Gate                                                                        |

|                                         | 🕨 🛑 AND Gate                                                                       |

| Circuit Pin Config                      | Not cate Creates a ga Opis can perform Add Opgrat AND Add operation B Sequencial C |

|                                         | 🝯 Other Comp                                                                       |

|                                         | 🥤 Control Unit                                                                     |

| T                                       | 🛢 Computer D                                                                       |

#### Instantiating a component contd..

Drop the component at desired position

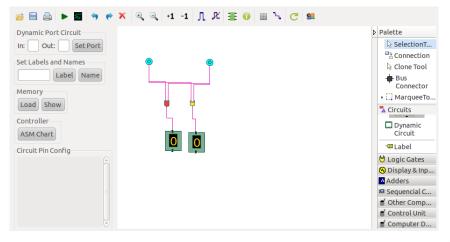

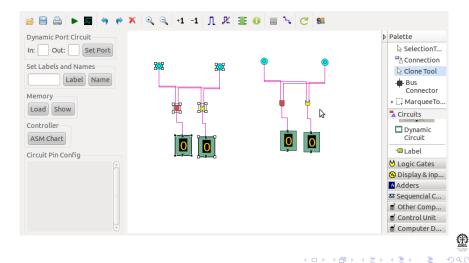

### **Connecting components**

#### left click on the connection tool

| 📔 🗎 🕨 🗖 🥱 🥐 🗙 🔍 G    | k +1 -1 Π K 🎚 🛈 🏾 🥆 C 😫 |                            |

|----------------------|-------------------------|----------------------------|

| Dynamic Port Circuit |                         | Palette                    |

| In: Out: Set Port    |                         | SelectionT                 |

| Set Labels and Names | a 0                     | Connection                 |

| Label Name           |                         | Connection<br>Bibe used to |

| Memory               |                         | Cothe various              |

| Load Show            | • •                     | Circuits                   |

| Controller           |                         | 💆 Logic Gates              |

| ASM Chart            |                         | 😔 Display & Inp            |

| Circuit Pin Config   |                         | 🛿 Bit Display              |

|                      |                         | Clock Pulse                |

|                      |                         | Bit Switch                 |

|                      |                         | Adders                     |

|                      |                         | 🛎 Sequencial C             |

|                      |                         | dther Comp                 |

|                      |                         | Control Unit               |

| Ū                    |                         | Computer D                 |

Э

#### Connecting components contd..

left click on the output terminal, move the mouse to the desired input terminal

#### Haff adder circuit

э

< ロ > < 同 > < 回 > < 回 >

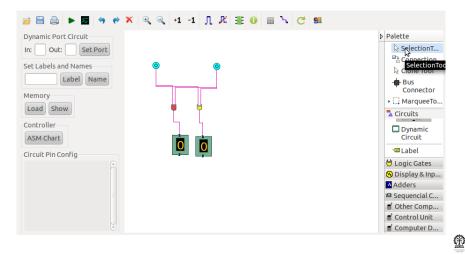

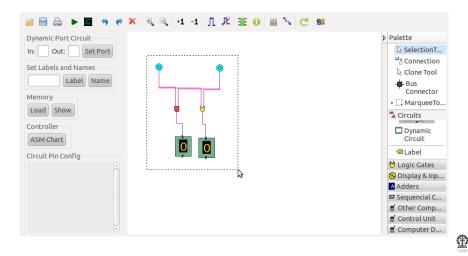

# **Clonning components**

#### left click on the selection tool

< ロ > < 同 > < 回 > < 回 >

э

### **Clonning components contd..**

Select the desired components to be clonned

18 / 36

э

<ロ> (日) (日) (日) (日) (日)

# **Clonning components contd..**

#### left click on the clone tool

# **Clonning components contd..**

#### Drag from any selected component

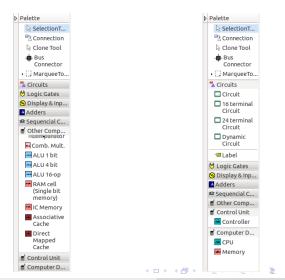

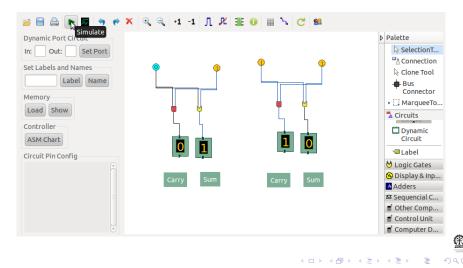

### Simulating circuits

Click on the Simulate button in the top toolbar

C Mandal, G Roy, D Ghosh (IIT Kharagpur)COAVL: A Virtual Lab on Computer Organi: COAVL-27February2015 21 / 36

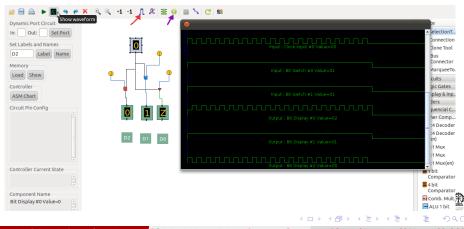

#### **Clock waveform**

- Click the Show waveform button to see the waveform

- 2 Red arrow indicates the bottun to start the clock

- **③** Violet arrow indicates the bottun to see the component name

C Mandal, G Roy, D Ghosh (IIT Kharagpur)COAVL: A Virtual Lab on Computer Organi: COAVL-27February2015 22 / 36

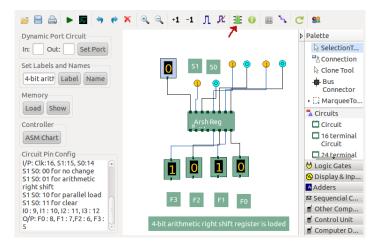

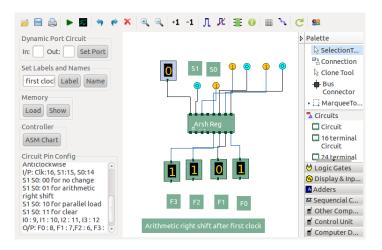

# Simulating sequential circuits

Red arrow indicates the bottun to see the pin configuration of a component

23 / 36

< ロ > < 同 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < 回 > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ > < □ >

### Simulating sequential circuits contd..

C Mandal, G Roy, D Ghosh (IIT Kharagpur COAVL: A Virtual Lab on Computer Organi: COAVL-27February2015

24 / 36

< ロ > < 同 > < 回 > < 回 >

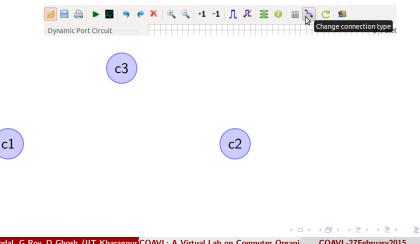

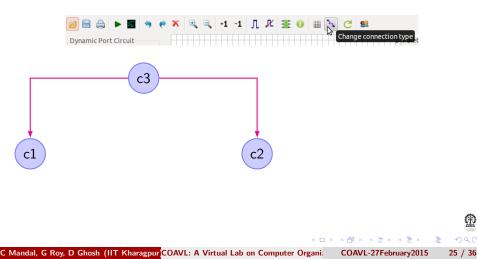

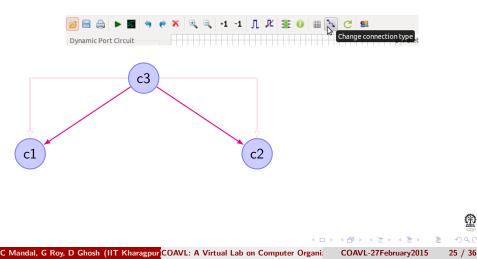

#### Change connection type

C Mandal, G Roy, D Ghosh (IIT Kharagpur)COAVL: A Virtual Lab on Computer Organia COAVL-27February2015 25 / 36

### Change connection type

### Change connection type

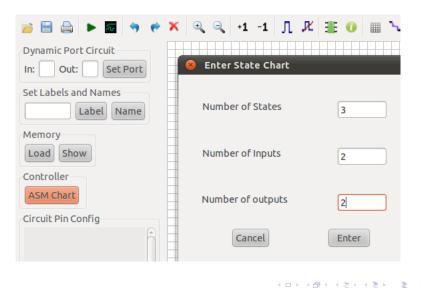

# Generating control sugnals from a given ASM chart

C Mandal, G Roy, D Ghosh (IIT Kharagpur)COAVL: A Virtual Lab on Computer Organia CO/

ani: COAVL-27February2015

# Generating control sugnals from a given ASM chart contd..

| 📂 🗃 🖨 🕨 🚾 🦘 🥐 🗙                                       | 🔍 🔍 +1 -1 👖 🎜 🏦 🕡 🏢 े         |

|-------------------------------------------------------|-------------------------------|

| Dynamic Port Circuit                                  |                               |

| In: Out: Set Port                                     | SWT Application               |

| Set Labels and Names                                  | Enter the name of the inputs  |

| Load Show                                             | input1 input2                 |

| Controller                                            |                               |

| ASM Chart                                             | Enter the name of the outputs |

| Circuit Pin Config                                    | out1 out2                     |

| C Mandal, G Roy, D Ghosh (IIT Kharagpur)COAVL: A Virt |                               |

# Generating control sugnals from a given ASM chart contd..

| 🧀 🗃 🚔 🕨 🖬 🥱 🥐           | ×                     | 🔍 -1 -1 Л Ж 🎚 🛛 🎟 🍾 С       |  |  |  |  |  |  |  |

|-------------------------|-----------------------|-----------------------------|--|--|--|--|--|--|--|

| Dynamic Port Circuit    |                       |                             |  |  |  |  |  |  |  |

| In: Out: Set Port       | t 😣 Enter State Table |                             |  |  |  |  |  |  |  |

| Set Labels and Names    | _                     | Inputs Outputs              |  |  |  |  |  |  |  |

| Label Name              | State                 | 00 01 10 11 out1 out2       |  |  |  |  |  |  |  |

| Memory                  | <b>S</b> 0            | S1 • S2 • S0 • S1 • 0 • 1 • |  |  |  |  |  |  |  |

| Load Show               | S1                    | S1 • S2 • S2 • S1 • 1 • 0 • |  |  |  |  |  |  |  |

| Controller<br>ASM Chart | S2                    | S2 v S2 v S2 v S0 v 0 v 1 v |  |  |  |  |  |  |  |

| Circuit Pin Config      | -                     | Enter                       |  |  |  |  |  |  |  |

|                         |                       |                             |  |  |  |  |  |  |  |

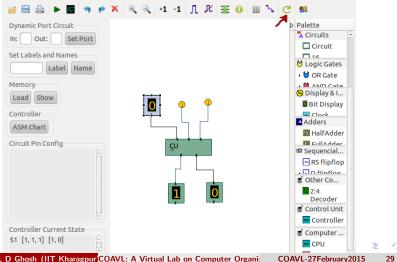

# Generating control sugnals from a given ASM chart contd..

Red arrow indicates the bottun to reset the controller

C Mandal, G Roy, D Ghosh (IIT Kharagpur COAVL: A Virtual Lab on Computer Organia

# Loading working memory to examine the behavior of the single instruction CPU component

| 🗃 🗃 🚔 🕨 🚾 🥱 🥐        | <b>X</b> 🔍 G | +1     | -1 Л J     | ۲ 🎟 | 0 | <b>`</b> C | 82      |       |                |   |

|----------------------|--------------|--------|------------|-----|---|------------|---------|-------|----------------|---|

| Dynamic Port Circuit | 😣 Load       | Memory | y Contents |     |   |            |         |       |                |   |

| In: Out: Set Port    | Address      | MSB    | LSB        |     |   | A          | Address | MSB   | LSB            |   |

| Set Labels and Names | 0000         |        |            |     |   |            | 1000    |       |                |   |

| Memory               | 0001         |        |            |     |   |            | 1001    |       |                |   |

| Load Show            | 0010         |        |            |     |   |            | 1010    |       |                |   |

| Controller           | 0011         |        |            |     |   |            | 1011    |       |                |   |

| ASM Chart            | 0100         |        |            |     |   |            | 1100    |       |                |   |

| Circuit Pin Config   | 0101         |        |            |     |   |            | 1101    |       |                |   |

| Â                    | 0110         |        |            |     |   |            | 1110    |       |                |   |

|                      | 0111         |        |            |     |   |            | 1111    |       |                |   |

| :<br>                |              | L      | oad Memor  | y   |   | Reset Me   | mory    |       | Load from file |   |

|                      |              |        |            |     |   |            |         |       |                |   |

|                      |              |        |            |     |   | < □        | • • €   | ] ▶ ∢ | ≣⊁ ∢ ≣ ⊁       | æ |

C Mandal, G Roy, D Ghosh (IIT Kharagpur)COAVL: A Virtual Lab on Computer Organi: COAVL-27February2015

# Showing working memory content at any point of time

| 🧀 🔒 🖿 🚾             | 🥱 🥐     | ×          | ⊇ +1   | -1 | лж | ∎ 0 | ·       | C S   |          |

|---------------------|---------|------------|--------|----|----|-----|---------|-------|----------|

| Dynamic Port Circui | 😣 Mem   | ory Conter | ıts.   | _  | _  | _   |         | _     |          |

| In: Out: S          | Address | MSB        | LSB    |    |    |     | Address | MSB   | LSB      |

| Set Labels and Name | 0000    | 10100010   | 10001  |    |    |     | 1000    | 00000 | 0000000  |

| Label               | 0001    | 1000000    | 00000  |    |    |     | 1001    | 00000 | 0000000  |

| Memory<br>Load Show | 0010    | 0000000    | 00000  |    |    |     | 1010    | 00000 | 0000000  |

| Controller          | 0011    | 00000000   | 00000  |    |    |     | 1011    | 00000 | 00000000 |

| ASM Chart           | 0100    | 00000000   | 000010 |    |    |     | 1100    | 00000 | 00000000 |

| Circuit Pin Config  | 0101    | 0000000    | 000101 |    |    |     | 1101    | 00000 | 00000000 |

|                     | 0110    | 0000000    | 00000  |    |    |     | 1110    | 00000 | 00000000 |

|                     | 0111    | 0000000    | 00000  |    |    |     | 1111    | 00000 | 0000000  |

|                     |         |            |        |    |    |     |         |       |          |

C Mandal, G Roy, D Ghosh (IIT Kharagpur)COAVL: A Virtual Lab on Computer Organi: COAVL-27February2015

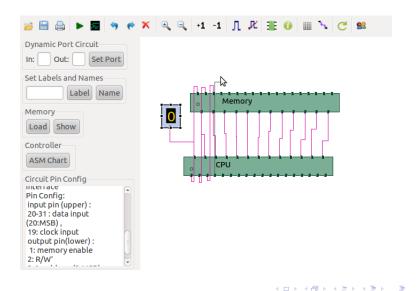

### Connecting the CPU with working memory

C Mandal, G Roy, D Ghosh (IIT Kharagpur COAVL: A Virtual Lab on Computer Organi COAVL-27February2015

# Saving components with identification

#### Click the save button

33 / 36

C Mandal, G Roy, D Ghosh (IIT Kharagpur)COAVL: A Virtual Lab on Computer Organi:

# Saving components with identification contd..

| 📷 📾 🕨 🖬 🦘 🥐 🗙 🔍 🔍 -1 -1 🞵 🕂 🏦 🕖 🏢                  |                    |                      |                                                            | 1                          |

|----------------------------------------------------|--------------------|----------------------|------------------------------------------------------------|----------------------------|

| Dynamic Port Circuit                               | Name: My           | Cktlogic             |                                                            | Palette                    |

| In: Out: Set Port                                  | Save in folder:    | :oa-vls              | ~                                                          | ► Selectio                 |

| Set Labels and Names                               | ▼ Browse for other |                      |                                                            | Connecti<br>Clone Tool     |

| Memory                                             | 🖣 🖆 coa-vls 🛅 🗖    | Desktop              | Create Folder                                              | Connector                  |

|                                                    | Places             | Name                 | Size Modified 👻 🏝                                          | → [] Marquee               |

|                                                    | Q Search           | ECLIPSE              | Monday 01 August 2011                                      | Circuits                   |

| Controller                                         | Recently Used      | 逼 coa website backup | Tuesday 09 August 2011                                     | Circuit                    |

| ASM Chart                                          | 🖀 coa-vls          | 🚞 cmake              | Tuesday 09 August 2011                                     | 💆 Logic Gates              |

| Circuit Pin Config                                 | Desktop            | 🚞 coa project        | Thursday 29 September 2011                                 | VOT Gate                   |

| 2:4 Decoder:                                       | File System        | a RegSlide           | Tuesday 18 October 2011                                    | • MOR Gate                 |

| Upper Terminals:Inputs<br>Bottom Terminals:Outputs | 105 GB File        | NetBeansProjects     | Thursday 31 May 2012                                       | Display & I                |

| Bottom Left Corper:                                | System Res         | tmp                  | Monday 03 September 2012<br>Wednesday 12 September 2012    | Display                    |

| Circle Represents pin-1                            | Documents          | ui-prevSit12sep      | Wednesday 12 September 2012<br>Wednesday 12 September 2012 | Adders                     |

| Numbering:Anticlockwise                            | Music              | eclipse              | Friday 28 September 2012                                   | 🗱 HalfAdder                |

| I/P: A0 : 5,A1 : 7<br>O/P: D0 : 4,D1 : 3.          | Pictures           | Videos               | Thursday 01 November 2012                                  | SullAddar                  |

| Controller Current State                           | Videos             | pdf                  | Friday 23 November 2012                                    | Sequencial                 |

| 0                                                  |                    |                      |                                                            | RS TUPTOP                  |

|                                                    | Add Remove         |                      | logic Files 🔹                                              | Other Co                   |

| Component Name                                     |                    |                      | Cancel                                                     | 2:4                        |

|                                                    |                    |                      | Concer 3                                                   | Decoder                    |

| AND Gate #1                                        |                    |                      |                                                            | Controller                 |

| User Identification                                |                    |                      |                                                            | Computer                   |

|                                                    |                    |                      |                                                            | COMPACE                    |

|                                                    |                    |                      |                                                            | 243                        |

|                                                    |                    |                      |                                                            | " VIGA KARANAN<br>DICEMPAN |

|                                                    |                    |                      | く ノロ く ノモ く ろうく                                            | =                          |

C Mandal, G Roy, D Ghosh (IIT Kharagpur<mark>COAVL: A Virtual Lab on Computer Organi: COAVL-27February2015 34 / 36</mark>

# Saving components with identification contd..

Click the Show User Id button to see identification in a saved file

C Mandal, G Roy, D Ghosh (IIT Kharagpur)COAVL: A Virtual Lab on Computer Organia C

COAVL-27February2015

Thank you!

C Mandal, G Roy, D Ghosh (IIT Kharagpur COAVL: A Virtual Lab on Computer Organi: COAVL-27February2015 36 / 36